#include <Code_Emitter.h>

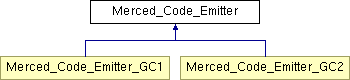

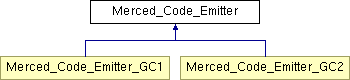

Inheritance diagram for Merced_Code_Emitter:

Public Member Functions | |

| Merced_Code_Emitter (tl::MemoryPool &m, unsigned byteCodeSize, unsigned nTargets) | |

| virtual | ~Merced_Code_Emitter () |

| void * | operator new (size_t sz, tl::MemoryPool &m) |

| void | operator delete (void *p, tl::MemoryPool &m) |

| void | flush_buffer () |

| unsigned | get_size () |

| void | copy (char *buffer) |

| void | set_bytecode_addr (unsigned bytecode_addr) |

| uint64 | code_check_sum () |

| void | set_mem_type_to_field_handle (void *field_handle, bool may_throw_exc=true) |

| void | set_mem_type_to_sp_offset (unsigned sp_offset) |

| void | set_mem_type_to_array_element_type (Java_Type type, bool may_throw_exc=true) |

| void | set_mem_type_to_method (bool may_throw_exc=true) |

| void | set_mem_type_to_switch () |

| void | set_mem_type_to_array_length (bool may_throw_exc=true) |

| void | set_mem_type_to_object_vt (bool may_throw_exc=true) |

| void | set_mem_type_to_vt_class (bool may_throw_exc=false) |

| void | set_mem_type_to_quick_thread (bool may_throw_exc=false) |

| void | next_two_instr_are_coupled (bool independent=true) |

| void | set_target (unsigned target_id) |

| void | set_switch_target (unsigned target_id, uint64 *abs_address_entry) |

| uint64 | get_target_offset (unsigned target_id) |

| void | memory_type_is_known () |

| void | memory_type_is_unknown () |

| void | allow_instruction_exchange () |

| void | disallow_instruction_exchange () |

| void | ipf_nop (EM_Syllable_Type tv, unsigned imm21=0) |

| void | ipf_add (unsigned dest, unsigned src1, unsigned src2, unsigned pred=0) |

| void | ipf_sub (unsigned dest, unsigned src1, unsigned src2, unsigned pred=0) |

| void | ipf_addp4 (unsigned dest, unsigned src1, unsigned src2, unsigned pred=0) |

| void | ipf_and (unsigned dest, unsigned src1, unsigned src2, unsigned pred=0) |

| void | ipf_or (unsigned dest, unsigned src1, unsigned src2, unsigned pred=0) |

| void | ipf_xor (unsigned dest, unsigned src1, unsigned src2, unsigned pred=0) |

| void | ipf_shladd (unsigned dest, unsigned src1, int count, unsigned src2, unsigned pred=0) |

| void | ipf_subi (unsigned dest, int imm, unsigned src, unsigned pred=0) |

| void | ipf_andi (unsigned dest, int imm8, unsigned src, unsigned pred=0) |

| void | ipf_ori (unsigned dest, int imm8, unsigned src, unsigned pred=0) |

| void | ipf_xori (unsigned dest, int imm, unsigned src, unsigned pred=0) |

| void | ipf_adds (unsigned dest, int imm14, unsigned src, unsigned pred=0) |

| void | ipf_addp4i (unsigned dest, int imm14, unsigned src, unsigned pred=0) |

| void | ipf_addl (unsigned dest, int imm22, unsigned src, unsigned pred=0) |

| void | ipf_cmp (Int_Comp_Rel cr, Compare_Extension cx, unsigned p1, unsigned p2, unsigned r2, unsigned r3, bool cmp4=false, unsigned pred=0) |

| void | ipf_cmpz (Int_Comp_Rel cr, Compare_Extension cx, unsigned p1, unsigned p2, unsigned r3, bool cmp4=false, unsigned pred=0) |

| void | ipf_cmpi (Int_Comp_Rel cr, Compare_Extension cx, unsigned p1, unsigned p2, int imm, unsigned r3, bool cmp4=false, unsigned pred=0) |

| void | ipf_movl (unsigned dest, unsigned upper_32, unsigned lower_32, unsigned pred=0) |

| void | ipf_movi64 (unsigned dest, uint64 imm64, unsigned pred=0) |

| void | ipf_brl_call (Branch_Prefetch_Hint ph, Branch_Whether_Hint wh, Branch_Dealloc_Hint dh, unsigned b1, uint64 imm64, unsigned pred=0) |

| void | ipf_brl_cond (Branch_Prefetch_Hint ph, Branch_Whether_Hint wh, Branch_Dealloc_Hint dh, uint64 imm64, unsigned pred=0) |

| void | ipf_movl_label (unsigned dest, unsigned target_id, unsigned pred=0) |

| void | ipf_extr (unsigned dest, unsigned src, int pos6, int len6, unsigned pred=0) |

| void | ipf_extru (unsigned dest, unsigned src, int pos6, int len6, unsigned pred=0) |

| void | ipf_depz (unsigned dest, unsigned src, int pos6, int len6, unsigned pred=0) |

| void | ipf_depiz (unsigned dest, int imm8, int pos6, int len6, unsigned pred=0) |

| void | ipf_depi (unsigned dest, int imm1, unsigned src, int pos6, int len6, unsigned pred=0) |

| void | ipf_dep (unsigned dest, unsigned r2, unsigned r3, int pos6, int len4, unsigned pred=0) |

| void | ipf_br (Branch_Type btype, Branch_Prefetch_Hint ph, Branch_Whether_Hint wh, Branch_Dealloc_Hint dh, unsigned target_id, unsigned pred=0) |

| void | ipf_brcall (Branch_Prefetch_Hint ph, Branch_Whether_Hint wh, Branch_Dealloc_Hint dh, unsigned b1, unsigned target25, unsigned pred=0) |

| void | ipf_bri (Branch_Type btype, Branch_Prefetch_Hint ph, Branch_Whether_Hint wh, Branch_Dealloc_Hint dh, unsigned b2, unsigned pred=0) |

| void | ipf_brret (Branch_Prefetch_Hint ph, Branch_Whether_Hint wh, Branch_Dealloc_Hint dh, unsigned b2, unsigned pred=0) |

| void | ipf_bricall (Branch_Prefetch_Hint ph, Branch_Whether_Hint wh, Branch_Dealloc_Hint dh, unsigned b1, unsigned b2, unsigned pred=0) |

| void | ipf_ld (Int_Mem_Size size, Ld_Flag flag, Mem_Hint hint, unsigned dest, unsigned addrreg, unsigned pred=0) |

| void | ipf_ld_inc_reg (Int_Mem_Size size, Ld_Flag flag, Mem_Hint hint, unsigned dest, unsigned addrreg, unsigned inc_reg, unsigned pred=0) |

| void | ipf_ld_inc_imm (Int_Mem_Size size, Ld_Flag flag, Mem_Hint hint, unsigned dest, unsigned addrreg, unsigned inc_imm, unsigned pred=0) |

| void | ipf_st (Int_Mem_Size size, St_Flag flag, Mem_Hint hint, unsigned addrreg, unsigned src, unsigned pred=0) |

| void | ipf_st_inc_imm (Int_Mem_Size size, St_Flag flag, Mem_Hint hint, unsigned addrreg, unsigned src, unsigned inc_imm, unsigned pred=0) |

| void | ipf_ldf (Float_Mem_Size size, Ld_Flag flag, Mem_Hint hint, unsigned dest, unsigned addrreg, unsigned pred=0) |

| void | ipf_ldf_inc_reg (Float_Mem_Size size, Ld_Flag flag, Mem_Hint hint, unsigned dest, unsigned addrreg, unsigned inc_reg, unsigned pred=0) |

| void | ipf_ldf_inc_imm (Float_Mem_Size size, Ld_Flag flag, Mem_Hint hint, unsigned dest, unsigned addrreg, unsigned inc_imm, unsigned pred=0) |

| void | ipf_stf (Float_Mem_Size size, St_Flag flag, Mem_Hint hint, unsigned addrreg, unsigned src, unsigned pred=0) |

| void | ipf_stf_inc_imm (Float_Mem_Size size, St_Flag flag, Mem_Hint hint, unsigned addrreg, unsigned src, unsigned inc_imm, unsigned pred=0) |

| void | ipf_mov (unsigned dest, unsigned src, unsigned pred=0) |

| void | ipf_movi (unsigned dest, int imm22, unsigned pred=0) |

| void | ipf_neg (unsigned dest, unsigned src, unsigned pred=0) |

| void | ipf_sxt (Sxt_Size size, unsigned dest, unsigned src, unsigned pred=0) |

| void | ipf_zxt (Sxt_Size size, unsigned dest, unsigned src, unsigned pred=0) |

| void | ipf_shl (unsigned dest, unsigned src1, unsigned src2, unsigned pred=0) |

| void | ipf_shr (unsigned dest, unsigned src1, unsigned src2, unsigned pred=0) |

| void | ipf_shru (unsigned dest, unsigned src1, unsigned src2, unsigned pred=0) |

| void | ipf_shli (unsigned dest, unsigned src1, int count, unsigned pred=0) |

| void | ipf_shri (unsigned dest, unsigned src1, int count, unsigned pred=0) |

| void | ipf_shrui (unsigned dest, unsigned src1, int count, unsigned pred=0) |

| void | ipf_setf (FReg_Convert form, unsigned fdest, unsigned src, unsigned pred=0) |

| void | ipf_getf (FReg_Convert form, unsigned dest, unsigned fsrc, unsigned pred=0) |

| void | ipf_fma (Float_Precision pc, Float_Status_Field sf, unsigned dest, unsigned src1, unsigned src2, unsigned src3, unsigned pred=0) |

| void | ipf_fnma (Float_Precision pc, Float_Status_Field sf, unsigned dest, unsigned src1, unsigned src2, unsigned src3, unsigned pred=0) |

| void | ipf_fms (Float_Precision pc, Float_Status_Field sf, unsigned dest, unsigned src1, unsigned src2, unsigned src3, unsigned pred=0) |

| void | ipf_frcpa (Float_Status_Field sf, unsigned dest, unsigned p2, unsigned src1, unsigned src2, unsigned pred=0) |

| void | ipf_fadd (Float_Precision pc, unsigned dest, unsigned src1, unsigned src2, unsigned pred=0) |

| void | ipf_fsub (Float_Precision pc, unsigned dest, unsigned src1, unsigned src2, unsigned pred=0) |

| void | ipf_fmul (Float_Precision pc, unsigned dest, unsigned src1, unsigned src2, unsigned pred=0) |

| void | ipf_fnorm (Float_Precision pc, unsigned dest, unsigned src, unsigned pred=0) |

| void | ipf_fmerge (Float_Merge fm, unsigned dest, unsigned src1, unsigned src2, unsigned pred=0) |

| void | ipf_fcmp (Float_Comp_Rel cr, Compare_Extension cx, unsigned p1, unsigned p2, unsigned f2, unsigned f3, unsigned pred=0) |

| void | ipf_fclass (Compare_Extension cx, unsigned p1, unsigned p2, unsigned f2, unsigned fclass9, unsigned pred=0) |

| void | ipf_fcvt_fx (FFix_Convert fc, Float_Status_Field sf, unsigned dest, unsigned src, unsigned pred=0) |

| void | ipf_fcvt_xf (unsigned dest, unsigned src, unsigned pred=0) |

| void | ipf_fmov (unsigned dest, unsigned src, unsigned pred=0) |

| void | ipf_fneg (unsigned dest, unsigned src, unsigned pred=0) |

| void | ipf_alloc (unsigned dest, unsigned i, unsigned l, unsigned o, unsigned r) |

| void | ipf_mtbr_michal (unsigned bdest, unsigned src, bool ret=false, unsigned offset=0, unsigned pred=0) |

| void | ipf_mtbr (unsigned bdest, unsigned src, unsigned pred=0) |

| void | ipf_mfbr (unsigned dest, unsigned bsrc, unsigned pred=0) |

| void | ipf_mtap (EM_Application_Register adest, unsigned src, unsigned pred=0) |

| void | ipf_mfap (unsigned dest, EM_Application_Register asrc, unsigned pred=0) |

| void | ipf_movip (unsigned dest, unsigned pred=0) |

| void | ipf_xma (unsigned dest, unsigned src1, unsigned src2, unsigned src3, Xla_Flag flag, unsigned pred=0) |

| void | ipf_cmpxchg (Int_Mem_Size size, Cmpxchg_Flag flag, Mem_Hint hint, unsigned dest, unsigned r3, unsigned r2, unsigned pred=0) |

| void | ipf_mtpr (unsigned src1, unsigned mask17=0x1ffff, unsigned pred=0) |

| void | ipf_mfpr (unsigned dest, unsigned pred=0) |

| void | ipf_cover () |

| void | ipf_flushrs () |

| void | ipf_mf (unsigned pred=0) |

Static Public Member Functions | |

| static unsigned | estimate_mem_size (unsigned byteCodeSize) |

| static char * | fix_code_buffer_address (char const *buf) |

Protected Member Functions | |

| virtual void | _init_ir (Encoder_Unscheduled_Instr_IR &ir, unsigned bytecode_addr, EM_Syllable_Type syl_type, unsigned pred) |

| virtual void | copy_ir_into_slot (Encoder_Instr_IR &dest, Encoder_Unscheduled_Instr_IR &src) |

| virtual void | copy_unscheduled_ir (Encoder_Unscheduled_Instr_IR &dest, Encoder_Unscheduled_Instr_IR &src) |

| void | _gen_an_IR_0_0 (unsigned bca, EM_Syllable_Type syl_type, unsigned pred) |

| void | _gen_an_IR_1i_2ii (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned idest_reg, unsigned isrc_reg1, unsigned isrc_reg2, bool mem_access=false) |

| void | _gen_an_IR_1i_1i (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned idest_reg, unsigned isrc_reg, bool mem_access=false) |

| void | _gen_an_IR_1i_0 (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned idest_reg) |

| void | _gen_an_IR_1i_ip (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned idest_reg) |

| void | _gen_an_IR_1i_allpp (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned idest_reg) |

| void | _gen_an_IR_allpp_1i (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned isrc_reg) |

| void | _gen_an_IR_2pp_2ii (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, Compare_Extension cx, unsigned dest_p1, unsigned dest_p2, unsigned isrc_reg1, unsigned isrc_reg2) |

| void | _gen_an_IR_2pp_1i (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, Compare_Extension cx, unsigned dest_p1, unsigned dest_p2, unsigned isrc_reg) |

| void | _gen_an_IR_2ii_2ii (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned idest_reg1, unsigned idest_reg2, unsigned isrc_reg1, unsigned isrc_reg2, bool mem_access=false) |

| void | _gen_an_IR_2ii_1i (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned idest_reg1, unsigned idest_reg2, unsigned isrc_reg, bool mem_access=false) |

| void | _gen_an_IR_0_2ii (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned isrc_reg1, unsigned isrc_reg2, bool mem_access=false) |

| void | _gen_an_IR_2fi_2ii (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned fdest_reg1, unsigned idest_reg2, unsigned isrc_reg1, unsigned isrc_reg2, bool mem_access=false) |

| void | _gen_an_IR_2fi_1i (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned fdest_reg1, unsigned idest_reg2, unsigned isrc_reg, bool mem_access=false) |

| void | _gen_an_IR_0_2fi (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned fsrc_reg1, unsigned isrc_reg2, bool mem_access=false) |

| void | _gen_an_IR_1i_2fi (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned idest_reg, unsigned fsrc_reg1, unsigned isrc_reg2, bool mem_access=false) |

| void | _gen_an_IR_1f_1f (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned fdest_reg, unsigned fsrc_reg) |

| void | _gen_an_IR_1f_2ff (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned fdest_reg, unsigned fsrc_reg1, unsigned fsrc_reg2) |

| void | _gen_an_IR_1f_3fff (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned fdest_reg, unsigned fsrc_reg1, unsigned fsrc_reg2, unsigned fsrc_reg3) |

| void | _gen_an_IR_2fp_2ff (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned fdest_reg, unsigned dest_p2, unsigned fsrc_reg1, unsigned fsrc_reg2) |

| void | _gen_an_IR_1i_1b (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned idest_reg, unsigned bsrc_reg) |

| void | _gen_an_IR_1b_1i (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned bdest_reg, unsigned isrc_reg) |

| void | _gen_an_IR_0_1b (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned bsrc_reg) |

| void | _gen_an_IR_1b_0 (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned bdest_reg) |

| void | _gen_an_IR_1b_1b (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned bdest_reg, unsigned bsrc_reg) |

| void | _gen_an_IR_1i_1f (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned idest_reg, unsigned fsrc_reg) |

| void | _gen_an_IR_1f_1i (unsigned bca, EM_Syllable_Type syl_type, unsigned pred, unsigned fdest_reg, unsigned isrc_reg, bool mem_access=false) |

| void * | _alloc_space (size_t) |

| void | _free_arena (apr_memnode_t *) |

| char * | _copy (char *buffer, apr_memnode_t *a) |

| Bundle_IR * | incr_wbuf_ptr (Bundle_IR *p) |

| Bundle_IR * | decr_wbuf_ptr (Bundle_IR *p) |

| Bundle_IR * | incr_wbuf_ptr_by (Bundle_IR *p, int k) |

| Instr_IR * | incr_slot_ptr (Instr_IR *p) |

| Instr_IR * | decr_slot_ptr (Instr_IR *p) |

| void | new_bundle () |

| void | new_bundle_with_no_emit () |

| virtual void | emit_bundle (Bundle_IR *bundle_ir) |

| void | prepass_before_emit (Bundle_IR *first, Bundle_IR *last) |

| void | emit_several_bundles (Bundle_IR *first, Bundle_IR *last) |

| void | emit_all () |

| void | buffer_overflow () |

| void | reset_mem_type () |

| void | schedule_an_IR_ne (Unsch_Instr_IR &ir) |

| void | schedule_an_IR_ex (Unsch_Instr_IR &ir) |

| void | schedule_an_IR (Encoder_Unscheduled_Instr_IR &ir) |

| void | place_instr_into_slot (Bundle_IR *bundle, int slot, Encoder_Unscheduled_Instr_IR &instr, unsigned need_stop) |

| bool | place_instr_into_bundle (Bundle_IR *bundle, Encoder_Unscheduled_Instr_IR &instr) |

| bool | instr_fits_into_slot (Bundle_IR *bundle, int slot, Unsch_Instr_IR &instr, unsigned &need_stop) |

| bool | instr_couple_fits_into_slots (Bundle_IR *bundle, unsigned slot1, unsigned slot2, Unsch_Instr_IR &instr1, Unsch_Instr_IR &instr2, unsigned &stop_pos) |

| void | place_instr_couple_into_slots (Bundle_IR *bundle, unsigned slot1, unsigned slot2, Unsch_Instr_IR &instr1, Unsch_Instr_IR &instr2, unsigned stop_pos) |

| Instr_IR * | place_instr_couple_into_bundle (Bundle_IR *bundle, Unsch_Instr_IR &instr1, Unsch_Instr_IR &instr2, bool unord) |

| void | schedule_two_IR_ne (Unsch_Instr_IR &ir1, Unsch_Instr_IR &ir2, bool unord) |

| void | schedule_two_IR_ex (Unsch_Instr_IR &ir1, Unsch_Instr_IR &ir2, bool unord) |

| void | apply_patches (char *code_buffer, uint64 *target_offset_tbl) |

| void | apply_brl_patches (char *code_buffer) |

| void | apply_brl_patch (MCE_brl_patch *patch, char *code_buffer) |

Protected Attributes | |

| tl::MemoryPool & | mem_pool |

| apr_allocator_t * | allocator |

| apr_memnode_t * | arena |

| Bundle_IR | wbuf [21] |

| Bundle_IR * | wbuf_first |

| Bundle_IR * | wbuf_last |

| Bundle_IR *const | wbuf_end |

| Instr_IR | slots [(21 *ENC_N_SLOTS)] |

| Instr_IR * | slot_end |

| int | last_empty_slot |

| Instr_IR * | gl_first_empty_slot |

| Instr_IR * | empty_slots [(21 *(ENC_N_SLOTS-1))] |

| Bundle_IR * | empty_bdls [21] |

| unsigned | n_targets |

| uint64 * | target_offset |

| bool | next_instr_is_target |

| unsigned | next_instr_target_id |

| bool | needs_patching |

| unsigned | patch_target_id |

| uint64 | curr_offset |

| Patch * | patches |

| MCE_brl_patch_list * | brl_patches |

| Byte | reg_map [ENC_N_REG] |

| Byte *const | ireg_map |

| Byte *const | freg_map |

| Byte *const | breg_map |

| Byte *const | areg_map |

| Byte *const | preg_map |

| int | n_fast_reg |

| Enc_All_Reg_BV | curr_wr_reg_vector |

| Enc_All_Reg_BV | curr_rd_reg_vector |

| bool | fast_reg_dep_check |

| unsigned | curr_bc_addr |

| Encoder_Memory_Type | curr_mem_type |

| uint64 | curr_mem_value |

| bool | curr_exc |

| bool | curr_is_mem_access |

| bool | wbuf_is_empty |

| Coupled_Instr_State | coupled_instr_state |

| bool | curr_instr_couple_is_unordered |

| bool | known_mem_type |

| bool | exch_instr |

| IPF_Encoder | encoder0 |

| IPF_Encoder * | encoder |

Static Protected Attributes | |

| static const uint16 | unavailable_tmplts [ST_last_type+1][2][ENC_N_SLOTS] |

| static const Byte | cmp_ext_to_special_instr [cmp_last] |

| Merced_Code_Emitter.Merced_Code_Emitter | ( | tl::MemoryPool & | m, | |

| unsigned | byteCodeSize, | |||

| unsigned | nTargets | |||

| ) |

| virtual Merced_Code_Emitter.~Merced_Code_Emitter | ( | ) | [virtual] |

| void* Merced_Code_Emitter.operator new | ( | size_t | sz, | |

| tl::MemoryPool & | m | |||

| ) |

Reimplemented in Merced_Code_Emitter_GC1, and Merced_Code_Emitter_GC2.

| void Merced_Code_Emitter.operator delete | ( | void * | p, | |

| tl::MemoryPool & | m | |||

| ) |

Reimplemented in Merced_Code_Emitter_GC1, and Merced_Code_Emitter_GC2.

| void Merced_Code_Emitter.flush_buffer | ( | ) |

| unsigned Merced_Code_Emitter.get_size | ( | ) |

| void Merced_Code_Emitter.copy | ( | char * | buffer | ) |

| static unsigned Merced_Code_Emitter.estimate_mem_size | ( | unsigned | byteCodeSize | ) | [static] |

| static char* Merced_Code_Emitter.fix_code_buffer_address | ( | char const * | buf | ) | [static] |

| void Merced_Code_Emitter.set_bytecode_addr | ( | unsigned | bytecode_addr | ) |

| uint64 Merced_Code_Emitter.code_check_sum | ( | ) |

| void Merced_Code_Emitter.set_mem_type_to_field_handle | ( | void * | field_handle, | |

| bool | may_throw_exc = true | |||

| ) |

| void Merced_Code_Emitter.set_mem_type_to_sp_offset | ( | unsigned | sp_offset | ) |

| void Merced_Code_Emitter.set_mem_type_to_array_element_type | ( | Java_Type | type, | |

| bool | may_throw_exc = true | |||

| ) |

| void Merced_Code_Emitter.set_mem_type_to_method | ( | bool | may_throw_exc = true |

) |

| void Merced_Code_Emitter.set_mem_type_to_switch | ( | ) |

| void Merced_Code_Emitter.set_mem_type_to_array_length | ( | bool | may_throw_exc = true |

) |

| void Merced_Code_Emitter.set_mem_type_to_object_vt | ( | bool | may_throw_exc = true |

) |

| void Merced_Code_Emitter.set_mem_type_to_vt_class | ( | bool | may_throw_exc = false |

) |

| void Merced_Code_Emitter.set_mem_type_to_quick_thread | ( | bool | may_throw_exc = false |

) |

| void Merced_Code_Emitter.next_two_instr_are_coupled | ( | bool | independent = true |

) |

| void Merced_Code_Emitter.set_target | ( | unsigned | target_id | ) |

Reimplemented in Merced_Code_Emitter_GC1.

| void Merced_Code_Emitter.set_switch_target | ( | unsigned | target_id, | |

| uint64 * | abs_address_entry | |||

| ) |

| uint64 Merced_Code_Emitter.get_target_offset | ( | unsigned | target_id | ) |

| void Merced_Code_Emitter.memory_type_is_known | ( | ) |

| void Merced_Code_Emitter.memory_type_is_unknown | ( | ) |

| void Merced_Code_Emitter.allow_instruction_exchange | ( | ) |

| void Merced_Code_Emitter.disallow_instruction_exchange | ( | ) |

| void Merced_Code_Emitter.ipf_nop | ( | EM_Syllable_Type | tv, | |

| unsigned | imm21 = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_add | ( | unsigned | dest, | |

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_sub | ( | unsigned | dest, | |

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_addp4 | ( | unsigned | dest, | |

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_and | ( | unsigned | dest, | |

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_or | ( | unsigned | dest, | |

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_xor | ( | unsigned | dest, | |

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_shladd | ( | unsigned | dest, | |

| unsigned | src1, | |||

| int | count, | |||

| unsigned | src2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_subi | ( | unsigned | dest, | |

| int | imm, | |||

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_andi | ( | unsigned | dest, | |

| int | imm8, | |||

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_ori | ( | unsigned | dest, | |

| int | imm8, | |||

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_xori | ( | unsigned | dest, | |

| int | imm, | |||

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_adds | ( | unsigned | dest, | |

| int | imm14, | |||

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_addp4i | ( | unsigned | dest, | |

| int | imm14, | |||

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_addl | ( | unsigned | dest, | |

| int | imm22, | |||

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_cmp | ( | Int_Comp_Rel | cr, | |

| Compare_Extension | cx, | |||

| unsigned | p1, | |||

| unsigned | p2, | |||

| unsigned | r2, | |||

| unsigned | r3, | |||

| bool | cmp4 = false, |

|||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_cmpz | ( | Int_Comp_Rel | cr, | |

| Compare_Extension | cx, | |||

| unsigned | p1, | |||

| unsigned | p2, | |||

| unsigned | r3, | |||

| bool | cmp4 = false, |

|||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_cmpi | ( | Int_Comp_Rel | cr, | |

| Compare_Extension | cx, | |||

| unsigned | p1, | |||

| unsigned | p2, | |||

| int | imm, | |||

| unsigned | r3, | |||

| bool | cmp4 = false, |

|||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_movl | ( | unsigned | dest, | |

| unsigned | upper_32, | |||

| unsigned | lower_32, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_movi64 | ( | unsigned | dest, | |

| uint64 | imm64, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_brl_call | ( | Branch_Prefetch_Hint | ph, | |

| Branch_Whether_Hint | wh, | |||

| Branch_Dealloc_Hint | dh, | |||

| unsigned | b1, | |||

| uint64 | imm64, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_brl_cond | ( | Branch_Prefetch_Hint | ph, | |

| Branch_Whether_Hint | wh, | |||

| Branch_Dealloc_Hint | dh, | |||

| uint64 | imm64, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_movl_label | ( | unsigned | dest, | |

| unsigned | target_id, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_extr | ( | unsigned | dest, | |

| unsigned | src, | |||

| int | pos6, | |||

| int | len6, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_extru | ( | unsigned | dest, | |

| unsigned | src, | |||

| int | pos6, | |||

| int | len6, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_depz | ( | unsigned | dest, | |

| unsigned | src, | |||

| int | pos6, | |||

| int | len6, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_depiz | ( | unsigned | dest, | |

| int | imm8, | |||

| int | pos6, | |||

| int | len6, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_depi | ( | unsigned | dest, | |

| int | imm1, | |||

| unsigned | src, | |||

| int | pos6, | |||

| int | len6, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_dep | ( | unsigned | dest, | |

| unsigned | r2, | |||

| unsigned | r3, | |||

| int | pos6, | |||

| int | len4, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_br | ( | Branch_Type | btype, | |

| Branch_Prefetch_Hint | ph, | |||

| Branch_Whether_Hint | wh, | |||

| Branch_Dealloc_Hint | dh, | |||

| unsigned | target_id, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_brcall | ( | Branch_Prefetch_Hint | ph, | |

| Branch_Whether_Hint | wh, | |||

| Branch_Dealloc_Hint | dh, | |||

| unsigned | b1, | |||

| unsigned | target25, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_bri | ( | Branch_Type | btype, | |

| Branch_Prefetch_Hint | ph, | |||

| Branch_Whether_Hint | wh, | |||

| Branch_Dealloc_Hint | dh, | |||

| unsigned | b2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_brret | ( | Branch_Prefetch_Hint | ph, | |

| Branch_Whether_Hint | wh, | |||

| Branch_Dealloc_Hint | dh, | |||

| unsigned | b2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_bricall | ( | Branch_Prefetch_Hint | ph, | |

| Branch_Whether_Hint | wh, | |||

| Branch_Dealloc_Hint | dh, | |||

| unsigned | b1, | |||

| unsigned | b2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_ld | ( | Int_Mem_Size | size, | |

| Ld_Flag | flag, | |||

| Mem_Hint | hint, | |||

| unsigned | dest, | |||

| unsigned | addrreg, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_ld_inc_reg | ( | Int_Mem_Size | size, | |

| Ld_Flag | flag, | |||

| Mem_Hint | hint, | |||

| unsigned | dest, | |||

| unsigned | addrreg, | |||

| unsigned | inc_reg, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_ld_inc_imm | ( | Int_Mem_Size | size, | |

| Ld_Flag | flag, | |||

| Mem_Hint | hint, | |||

| unsigned | dest, | |||

| unsigned | addrreg, | |||

| unsigned | inc_imm, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_st | ( | Int_Mem_Size | size, | |

| St_Flag | flag, | |||

| Mem_Hint | hint, | |||

| unsigned | addrreg, | |||

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_st_inc_imm | ( | Int_Mem_Size | size, | |

| St_Flag | flag, | |||

| Mem_Hint | hint, | |||

| unsigned | addrreg, | |||

| unsigned | src, | |||

| unsigned | inc_imm, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_ldf | ( | Float_Mem_Size | size, | |

| Ld_Flag | flag, | |||

| Mem_Hint | hint, | |||

| unsigned | dest, | |||

| unsigned | addrreg, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_ldf_inc_reg | ( | Float_Mem_Size | size, | |

| Ld_Flag | flag, | |||

| Mem_Hint | hint, | |||

| unsigned | dest, | |||

| unsigned | addrreg, | |||

| unsigned | inc_reg, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_ldf_inc_imm | ( | Float_Mem_Size | size, | |

| Ld_Flag | flag, | |||

| Mem_Hint | hint, | |||

| unsigned | dest, | |||

| unsigned | addrreg, | |||

| unsigned | inc_imm, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_stf | ( | Float_Mem_Size | size, | |

| St_Flag | flag, | |||

| Mem_Hint | hint, | |||

| unsigned | addrreg, | |||

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_stf_inc_imm | ( | Float_Mem_Size | size, | |

| St_Flag | flag, | |||

| Mem_Hint | hint, | |||

| unsigned | addrreg, | |||

| unsigned | src, | |||

| unsigned | inc_imm, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_mov | ( | unsigned | dest, | |

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_movi | ( | unsigned | dest, | |

| int | imm22, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_neg | ( | unsigned | dest, | |

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_sxt | ( | Sxt_Size | size, | |

| unsigned | dest, | |||

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_zxt | ( | Sxt_Size | size, | |

| unsigned | dest, | |||

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_shl | ( | unsigned | dest, | |

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_shr | ( | unsigned | dest, | |

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_shru | ( | unsigned | dest, | |

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_shli | ( | unsigned | dest, | |

| unsigned | src1, | |||

| int | count, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_shri | ( | unsigned | dest, | |

| unsigned | src1, | |||

| int | count, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_shrui | ( | unsigned | dest, | |

| unsigned | src1, | |||

| int | count, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_setf | ( | FReg_Convert | form, | |

| unsigned | fdest, | |||

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_getf | ( | FReg_Convert | form, | |

| unsigned | dest, | |||

| unsigned | fsrc, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_fma | ( | Float_Precision | pc, | |

| Float_Status_Field | sf, | |||

| unsigned | dest, | |||

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | src3, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_fnma | ( | Float_Precision | pc, | |

| Float_Status_Field | sf, | |||

| unsigned | dest, | |||

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | src3, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_fms | ( | Float_Precision | pc, | |

| Float_Status_Field | sf, | |||

| unsigned | dest, | |||

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | src3, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_frcpa | ( | Float_Status_Field | sf, | |

| unsigned | dest, | |||

| unsigned | p2, | |||

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_fadd | ( | Float_Precision | pc, | |

| unsigned | dest, | |||

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_fsub | ( | Float_Precision | pc, | |

| unsigned | dest, | |||

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_fmul | ( | Float_Precision | pc, | |

| unsigned | dest, | |||

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_fnorm | ( | Float_Precision | pc, | |

| unsigned | dest, | |||

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_fmerge | ( | Float_Merge | fm, | |

| unsigned | dest, | |||

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_fcmp | ( | Float_Comp_Rel | cr, | |

| Compare_Extension | cx, | |||

| unsigned | p1, | |||

| unsigned | p2, | |||

| unsigned | f2, | |||

| unsigned | f3, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_fclass | ( | Compare_Extension | cx, | |

| unsigned | p1, | |||

| unsigned | p2, | |||

| unsigned | f2, | |||

| unsigned | fclass9, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_fcvt_fx | ( | FFix_Convert | fc, | |

| Float_Status_Field | sf, | |||

| unsigned | dest, | |||

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_fcvt_xf | ( | unsigned | dest, | |

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_fmov | ( | unsigned | dest, | |

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_fneg | ( | unsigned | dest, | |

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_alloc | ( | unsigned | dest, | |

| unsigned | i, | |||

| unsigned | l, | |||

| unsigned | o, | |||

| unsigned | r | |||

| ) |

| void Merced_Code_Emitter.ipf_mtbr_michal | ( | unsigned | bdest, | |

| unsigned | src, | |||

| bool | ret = false, |

|||

| unsigned | offset = 0, |

|||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_mtbr | ( | unsigned | bdest, | |

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_mfbr | ( | unsigned | dest, | |

| unsigned | bsrc, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_mtap | ( | EM_Application_Register | adest, | |

| unsigned | src, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_mfap | ( | unsigned | dest, | |

| EM_Application_Register | asrc, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_movip | ( | unsigned | dest, | |

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_xma | ( | unsigned | dest, | |

| unsigned | src1, | |||

| unsigned | src2, | |||

| unsigned | src3, | |||

| Xla_Flag | flag, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_cmpxchg | ( | Int_Mem_Size | size, | |

| Cmpxchg_Flag | flag, | |||

| Mem_Hint | hint, | |||

| unsigned | dest, | |||

| unsigned | r3, | |||

| unsigned | r2, | |||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_mtpr | ( | unsigned | src1, | |

| unsigned | mask17 = 0x1ffff, |

|||

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_mfpr | ( | unsigned | dest, | |

| unsigned | pred = 0 | |||

| ) |

| void Merced_Code_Emitter.ipf_cover | ( | ) |

| void Merced_Code_Emitter.ipf_flushrs | ( | ) |

| void Merced_Code_Emitter.ipf_mf | ( | unsigned | pred = 0 |

) |

| virtual void Merced_Code_Emitter._init_ir | ( | Encoder_Unscheduled_Instr_IR & | ir, | |

| unsigned | bytecode_addr, | |||

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred | |||

| ) | [protected, virtual] |

| virtual void Merced_Code_Emitter.copy_ir_into_slot | ( | Encoder_Instr_IR & | dest, | |

| Encoder_Unscheduled_Instr_IR & | src | |||

| ) | [protected, virtual] |

| virtual void Merced_Code_Emitter.copy_unscheduled_ir | ( | Encoder_Unscheduled_Instr_IR & | dest, | |

| Encoder_Unscheduled_Instr_IR & | src | |||

| ) | [protected, virtual] |

| void Merced_Code_Emitter._gen_an_IR_0_0 | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_1i_2ii | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | idest_reg, | |||

| unsigned | isrc_reg1, | |||

| unsigned | isrc_reg2, | |||

| bool | mem_access = false | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_1i_1i | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | idest_reg, | |||

| unsigned | isrc_reg, | |||

| bool | mem_access = false | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_1i_0 | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | idest_reg | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_1i_ip | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | idest_reg | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_1i_allpp | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | idest_reg | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_allpp_1i | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | isrc_reg | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_2pp_2ii | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| Compare_Extension | cx, | |||

| unsigned | dest_p1, | |||

| unsigned | dest_p2, | |||

| unsigned | isrc_reg1, | |||

| unsigned | isrc_reg2 | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_2pp_1i | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| Compare_Extension | cx, | |||

| unsigned | dest_p1, | |||

| unsigned | dest_p2, | |||

| unsigned | isrc_reg | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_2ii_2ii | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | idest_reg1, | |||

| unsigned | idest_reg2, | |||

| unsigned | isrc_reg1, | |||

| unsigned | isrc_reg2, | |||

| bool | mem_access = false | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_2ii_1i | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | idest_reg1, | |||

| unsigned | idest_reg2, | |||

| unsigned | isrc_reg, | |||

| bool | mem_access = false | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_0_2ii | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | isrc_reg1, | |||

| unsigned | isrc_reg2, | |||

| bool | mem_access = false | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_2fi_2ii | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | fdest_reg1, | |||

| unsigned | idest_reg2, | |||

| unsigned | isrc_reg1, | |||

| unsigned | isrc_reg2, | |||

| bool | mem_access = false | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_2fi_1i | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | fdest_reg1, | |||

| unsigned | idest_reg2, | |||

| unsigned | isrc_reg, | |||

| bool | mem_access = false | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_0_2fi | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | fsrc_reg1, | |||

| unsigned | isrc_reg2, | |||

| bool | mem_access = false | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_1i_2fi | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | idest_reg, | |||

| unsigned | fsrc_reg1, | |||

| unsigned | isrc_reg2, | |||

| bool | mem_access = false | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_1f_1f | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | fdest_reg, | |||

| unsigned | fsrc_reg | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_1f_2ff | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | fdest_reg, | |||

| unsigned | fsrc_reg1, | |||

| unsigned | fsrc_reg2 | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_1f_3fff | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | fdest_reg, | |||

| unsigned | fsrc_reg1, | |||

| unsigned | fsrc_reg2, | |||

| unsigned | fsrc_reg3 | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_2fp_2ff | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | fdest_reg, | |||

| unsigned | dest_p2, | |||

| unsigned | fsrc_reg1, | |||

| unsigned | fsrc_reg2 | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_1i_1b | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | idest_reg, | |||

| unsigned | bsrc_reg | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_1b_1i | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | bdest_reg, | |||

| unsigned | isrc_reg | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_0_1b | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | bsrc_reg | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_1b_0 | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | bdest_reg | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_1b_1b | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | bdest_reg, | |||

| unsigned | bsrc_reg | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_1i_1f | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | idest_reg, | |||

| unsigned | fsrc_reg | |||

| ) | [protected] |

| void Merced_Code_Emitter._gen_an_IR_1f_1i | ( | unsigned | bca, | |

| EM_Syllable_Type | syl_type, | |||

| unsigned | pred, | |||

| unsigned | fdest_reg, | |||

| unsigned | isrc_reg, | |||

| bool | mem_access = false | |||

| ) | [protected] |

| void* Merced_Code_Emitter._alloc_space | ( | size_t | ) | [protected] |

| void Merced_Code_Emitter._free_arena | ( | apr_memnode_t * | ) | [protected] |

| char* Merced_Code_Emitter._copy | ( | char * | buffer, | |

| apr_memnode_t * | a | |||

| ) | [protected] |

| void Merced_Code_Emitter.new_bundle | ( | ) | [protected] |

| void Merced_Code_Emitter.new_bundle_with_no_emit | ( | ) | [protected] |

| virtual void Merced_Code_Emitter.emit_bundle | ( | Bundle_IR * | bundle_ir | ) | [protected, virtual] |

| void Merced_Code_Emitter.emit_all | ( | ) | [protected] |

| void Merced_Code_Emitter.buffer_overflow | ( | ) | [protected] |

| void Merced_Code_Emitter.reset_mem_type | ( | ) | [protected] |

| void Merced_Code_Emitter.schedule_an_IR_ne | ( | Unsch_Instr_IR & | ir | ) | [protected] |

| void Merced_Code_Emitter.schedule_an_IR_ex | ( | Unsch_Instr_IR & | ir | ) | [protected] |

| void Merced_Code_Emitter.schedule_an_IR | ( | Encoder_Unscheduled_Instr_IR & | ir | ) | [protected] |

| void Merced_Code_Emitter.place_instr_into_slot | ( | Bundle_IR * | bundle, | |

| int | slot, | |||

| Encoder_Unscheduled_Instr_IR & | instr, | |||

| unsigned | need_stop | |||

| ) | [protected] |

| bool Merced_Code_Emitter.place_instr_into_bundle | ( | Bundle_IR * | bundle, | |

| Encoder_Unscheduled_Instr_IR & | instr | |||

| ) | [protected] |

| bool Merced_Code_Emitter.instr_fits_into_slot | ( | Bundle_IR * | bundle, | |

| int | slot, | |||

| Unsch_Instr_IR & | instr, | |||

| unsigned & | need_stop | |||

| ) | [protected] |

| bool Merced_Code_Emitter.instr_couple_fits_into_slots | ( | Bundle_IR * | bundle, | |

| unsigned | slot1, | |||

| unsigned | slot2, | |||

| Unsch_Instr_IR & | instr1, | |||

| Unsch_Instr_IR & | instr2, | |||

| unsigned & | stop_pos | |||

| ) | [protected] |

| void Merced_Code_Emitter.place_instr_couple_into_slots | ( | Bundle_IR * | bundle, | |

| unsigned | slot1, | |||

| unsigned | slot2, | |||

| Unsch_Instr_IR & | instr1, | |||

| Unsch_Instr_IR & | instr2, | |||

| unsigned | stop_pos | |||

| ) | [protected] |

| Instr_IR* Merced_Code_Emitter.place_instr_couple_into_bundle | ( | Bundle_IR * | bundle, | |

| Unsch_Instr_IR & | instr1, | |||

| Unsch_Instr_IR & | instr2, | |||

| bool | unord | |||

| ) | [protected] |

| void Merced_Code_Emitter.schedule_two_IR_ne | ( | Unsch_Instr_IR & | ir1, | |

| Unsch_Instr_IR & | ir2, | |||

| bool | unord | |||

| ) | [protected] |

| void Merced_Code_Emitter.schedule_two_IR_ex | ( | Unsch_Instr_IR & | ir1, | |

| Unsch_Instr_IR & | ir2, | |||

| bool | unord | |||

| ) | [protected] |

| void Merced_Code_Emitter.apply_patches | ( | char * | code_buffer, | |

| uint64 * | target_offset_tbl | |||

| ) | [protected] |

| void Merced_Code_Emitter.apply_brl_patches | ( | char * | code_buffer | ) | [protected] |

| void Merced_Code_Emitter.apply_brl_patch | ( | MCE_brl_patch * | patch, | |

| char * | code_buffer | |||

| ) | [protected] |

tl::MemoryPool& Merced_Code_Emitter.mem_pool [protected] |

apr_allocator_t* Merced_Code_Emitter.allocator [protected] |

apr_memnode_t* Merced_Code_Emitter.arena [protected] |

Bundle_IR Merced_Code_Emitter.wbuf[21] [protected] |

Bundle_IR* Merced_Code_Emitter.wbuf_first [protected] |

Bundle_IR* Merced_Code_Emitter.wbuf_last [protected] |

Bundle_IR* const Merced_Code_Emitter.wbuf_end [protected] |

Instr_IR Merced_Code_Emitter.slots[(21 *ENC_N_SLOTS)] [protected] |

Instr_IR* Merced_Code_Emitter.slot_end [protected] |

int Merced_Code_Emitter.last_empty_slot [protected] |

Instr_IR* Merced_Code_Emitter.gl_first_empty_slot [protected] |

Instr_IR* Merced_Code_Emitter.empty_slots[(21 *(ENC_N_SLOTS-1))] [protected] |

Bundle_IR* Merced_Code_Emitter.empty_bdls[21] [protected] |

unsigned Merced_Code_Emitter.n_targets [protected] |

uint64* Merced_Code_Emitter.target_offset [protected] |

bool Merced_Code_Emitter.next_instr_is_target [protected] |

unsigned Merced_Code_Emitter.next_instr_target_id [protected] |

bool Merced_Code_Emitter.needs_patching [protected] |

unsigned Merced_Code_Emitter.patch_target_id [protected] |

uint64 Merced_Code_Emitter.curr_offset [protected] |

Patch* Merced_Code_Emitter.patches [protected] |

MCE_brl_patch_list* Merced_Code_Emitter.brl_patches [protected] |

Byte Merced_Code_Emitter.reg_map[ENC_N_REG] [protected] |

Byte* const Merced_Code_Emitter.ireg_map [protected] |

Byte* const Merced_Code_Emitter.freg_map [protected] |

Byte* const Merced_Code_Emitter.breg_map [protected] |

Byte* const Merced_Code_Emitter.areg_map [protected] |

Byte* const Merced_Code_Emitter.preg_map [protected] |

int Merced_Code_Emitter.n_fast_reg [protected] |

Enc_All_Reg_BV Merced_Code_Emitter.curr_wr_reg_vector [protected] |

Enc_All_Reg_BV Merced_Code_Emitter.curr_rd_reg_vector [protected] |

bool Merced_Code_Emitter.fast_reg_dep_check [protected] |

const uint16 Merced_Code_Emitter.unavailable_tmplts[ST_last_type+1][2][ENC_N_SLOTS] [static, protected] |

unsigned Merced_Code_Emitter.curr_bc_addr [protected] |

Encoder_Memory_Type Merced_Code_Emitter.curr_mem_type [protected] |

uint64 Merced_Code_Emitter.curr_mem_value [protected] |

bool Merced_Code_Emitter.curr_exc [protected] |

bool Merced_Code_Emitter.curr_is_mem_access [protected] |

bool Merced_Code_Emitter.wbuf_is_empty [protected] |

bool Merced_Code_Emitter.curr_instr_couple_is_unordered [protected] |

const Byte Merced_Code_Emitter.cmp_ext_to_special_instr[cmp_last] [static, protected] |

bool Merced_Code_Emitter.known_mem_type [protected] |

bool Merced_Code_Emitter.exch_instr [protected] |

IPF_Encoder Merced_Code_Emitter.encoder0 [protected] |

IPF_Encoder * Merced_Code_Emitter.encoder [protected] |

Genereated on Tue Mar 11 19:26:02 2008 by Doxygen.

(c) Copyright 2005, 2008 The Apache Software Foundation or its licensors, as applicable.